IOPROB

ELECTRONIC SYSTEMS AUTOMATIC TEST,

DIAGNOSTIC AND REPAIR EXPERT SYSTEM (SISTEMA EXPERTO DE DIAGNÓSTICO AUTOMÁTICO Y REPARACIÓN DE SISTEMAS ELECTRÓNICOS).

Raimundo Rodulfo

|

|

Sistema electrónico de diagnóstico y análisis automatizado de fallas para sistemas IOP de conmutación digital. Sistema experto extendible a cualquier ambiente de

hardware.

Especificaciones:

· Capaz de detectar fallas a nivel de los componentes principales del sistema (microprocesador y chips periféricos de soporte), así como en la lógica digital TTL, y

en los demás componentes de la circuitería.

· Funcionamiento interactivo con el usuario, indicando a éste los posibles orígenes de las fallas detectadas, y guiando la metodología a seguir en la reparación.

· Diseñado con el menor hardware posible.

1. Elaborar un programa de diagnóstico en lenguaje de bajo nivel del microprocesador 8086, que resida en un firmware (EPROM), a ser insertado en alguno de

los sockets de la ROM de la tarjeta IOP en prueba (retirando las memorias del programa original de la tarjeta previamente). Este programa envía datos a un PC (a

través de una interfaz diseñada especialmente para este fín), que son procesados por un software de alto nivel, que proporciona información del estado de la

tarjeta, y propone métodos para reparar la falla detectada al personal técnico o especializado que lo utilice, a manera de un sistema experto.

Ventajas:

· Aprovecha el hardware de la tarjeta IOP.

· No exige conocer el protocolo de acceso a la tarjeta por el MultiBús para ejecutar las rutinas de autodiagnóstico.

Desventajas:

· La tarjeta IOP fué diseñada para funcionar dentro de un sistema mayor, con otras tarjetas inteligentes, comunicadas entre sí a través de un MultiBús, por lo cual

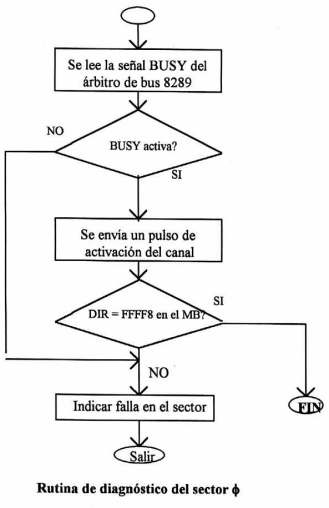

se presentan numerosas dificultades para hacerla funcionar y comunicar con el exterior de manera autónoma. Por otra parte, la presencia de los chips IOP 8089 y

árbitro de bús 8289 complica mas aún la situación, pués están configurados para responder a señales y comandos externos provenientes del MultiBús.

· Esta alternativa no permite localizar con exactitud fallas a nivel de la lógica TTL de la tarjeta.

2. Diseñar un módulo que simule las señales del MultiBús, y que se conecte a la tarjeta, de manera tal que se puedan enviar órdenes al IOP 8089 y al árbitro de

bús 8289 para direccionar los elementos del sistema y probarlos. Este sistema puede tener, a su vez, un puerto de comunicación con un PC, de forma de

interactuar con un software que sirva de interfaz con el usuario.

Ventajas:

· Permite una comunicación con la tarjeta desde el exterior, a través del MultiBús, pudiéndose obtener y suministrar información de y a la tarjeta mediante los

recursos de comunicación propios de la IOP.

Desventajas:

· Involucra un mayor y mas complejo diseño de hardware, para poder manejar todas las señales de control, direcciones y datos del MultiBús desde el exterior.

· No permite localizar con exactitud fallas a nivel de la lógica TTL de la tarjeta.

3. Diseñar un sistema que emule el funcionamiento del microprocesador 8086, y se conecte a la tarjeta a través de una base que se insertaría en el socket del 8086

(retirando el componente previamente), y que tendría cableadas todas las señales de interés, que permitirían controlar los componentes de la tarjeta desde el

exterior, y realizar las pruebas deseadas.

Ventajas:

· Idem que 1.

Desventajas:

· Requiere un diseño de hardware grande y complejo, que permita generar todas las señales de control, direcciones y datos del microprocesador 8086. Requiere

además lograr la sincronización con el reloj del sistema.

· Al igual que 1. y 2., no localiza con exactitud fallas a nivel de la lógica digital TTL.

La solución adoptada al problema planteado necesita, para satisfacer plenamente las especificaciones del proyecto, tomar elementos de las alternativas 1. y 2., y

complementar las deficiencias que éstas presentan en la detección de fallas a nivel de la lógica TTL de la tarjeta IOP, con el desarrollo simultáneo de un software

de alto nivel que será capaz de tomar decisiones en base a las fallas detectadas, y guiar al usuario en el camino mas conveniente para la reparación de las mismas.

Esto responde al hecho que la detección automática de fallas en circuitos digitales con componentes de media escala de integración (TTL y similares), involucra el

seguimiento y procesamiento de un gran número de señales, lo que amerita utilizar sistemas muy complejos, con múltiples entradas y salidas, y capaces de ser

configurados de distintas formas, vía software. El diseño de un sistema de estas características escapa al alcance del proyecto encomendado, y requiere de un

enorme desarrollo de hardware y software, que además involucra una mayor preparación del personal que lo utilice, y un tiempo mayor de conexión del equipo,

con mayores probabilidades de error. Esto enfoca la solución del problema hacia el desarrollo de un sistema experto (Inteligencia Artificial), que esté cargado con

toda la información de la tarjeta IOP relevante para su reparación, y que interactúe a través de una interfaz, especialmente diseñada, con un programa de

autodiagnóstico grabado en un firmware a ser insertado en la tarjeta (ver opción 1.), el cual enviará los resultados del diagnóstico automático de la tarjeta al

software, que los procesará y a partir de ellos tomará decisiones, para indicar al usuario el procedimiento mas adecuado de reparación, a manera de tutorial, con

un despliegue gráfico lo suficientemente ilustrativo de los resultados del diagnóstico y de los pasos a seguir. El sistema experto contará, para estos efectos, con una

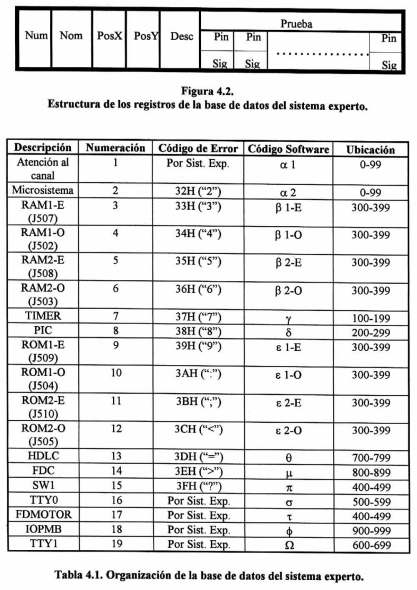

base de datos con información de los componentes de la tarjeta, las señales asociadas a sus pines en las distintas condiciones de prueba, y las posibles fallas, que

será utilizada para indicar al usuario el comportamiento esperado de los elementos del sector donde se ha localizado la falla, y de este modo permitirle detectar con

exactitud las causas, a nivel de la lógica TTL

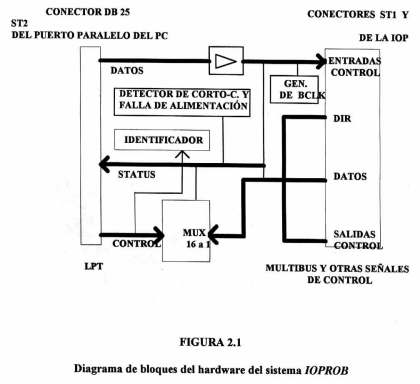

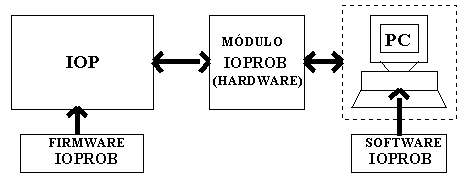

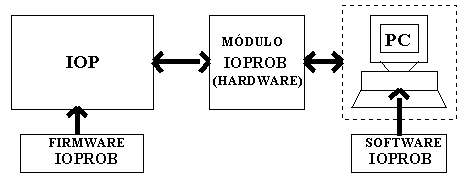

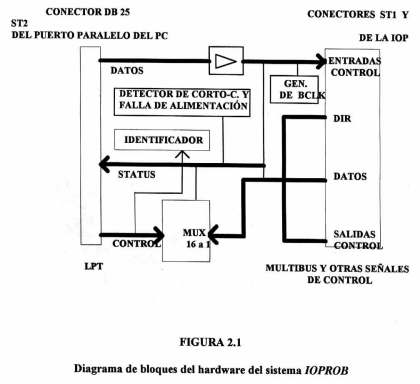

A continuación se muestra un diagrama de bloques del sistema:

Fig. 1

IOPROB

SISTEMA EXPERTO DE DIAGNÓSTICO Y REPARACIÓN DEL SISTEMA IOP

EJEMPLO: SIEMENS PABX EMS 601

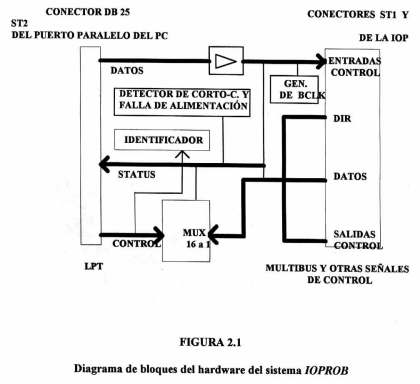

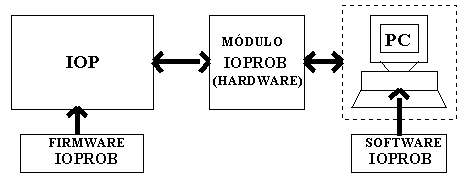

El hardware del sistema de diagnóstico consiste en un módulo electrónico de interfaz entre la tarjeta IOP y el microcomputador, que se encarga de las siguientes

funciones:

· Suministrar a la IOP todas las alimentaciones que ésta requiere para su funcionamiento (GND, +5 V, +12 V, -12 V DC). Para ello, dispondrá de una entrada de

alimentación de +5 V y una entrada de tierra, que se conectarán a una alimentación externa (fuente regulada de tensión contínua); y poseerá un componente de

interfaz para manejo de los niveles de protocolo RS-232C (el MAX233 de la MAXIM), el cual generará los niveles de ±12 V para los Line Drivers y los Line

Receivers (75150 y 75154) de la IOP.

· Comunicar el PC con la IOP a través del puerto paralelo (LPT). Esto se hará, a través de un cable DB25 que irá al puerto del computador, y que cableará en el

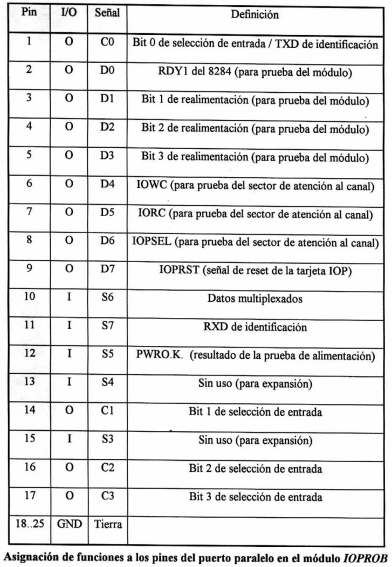

módulo de prueba las líneas de los puertos de datos, status y control del LPT, las cuales se utilizarán de la siguiente manera:

Control :

Servirán para seleccionar la función a ejecutar desde el computador. Esto se implementará con un decodificador (74LS138), el cual permitirá controlar la

habilitación de unos buffers tri-states que tendrán sus salidas cableadas a los conectores que van a la IOP.

Datos:

Las líneas del puerto de datos se utilizarán para enviar las señales que la tarjeta IOP requiere del exterior para inicializarse o comunicarse (RESET, BREQ, BUSY,

etc.) y otras señales o datos que se requieran, por el módulo IOPROB o por la IOP.

Status:

Estas líneas permitirán leer datos y recibir señales generadas por la IOP o el módulo IOPROB.

· Detectar fallas en la alimentación y corto-circuitos en la IOP. Esto se implementará con un circuito discreto analógico (basado en un BJT y una red pasiva), que

tendrá una entrada y una salida digital conectadas al puerto paralelo, que permitirán al comienzo de la prueba detectar fallas de esa índole.

· Identificar el puerto paralelo al que está conectado el módulo IOPROB. Para ello, se implementará un puerto de acceso en el módulo, cuya entrada estará

cableada a niveles fijos (palabra de identificación), y cuya salida podrá ser leída a través del puerto de status por el programa de alto nivel, y así determinar el

puerto utilizado y su dirección (LPT1,2 o 3). Esto se hace con la finalidad de evitar al usuario el chequeo de la dirección del puerto utilizado.

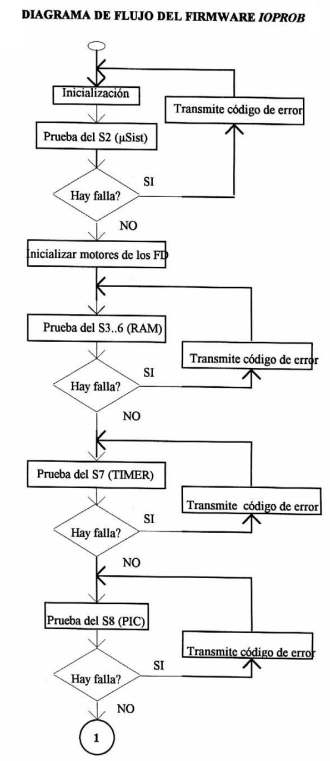

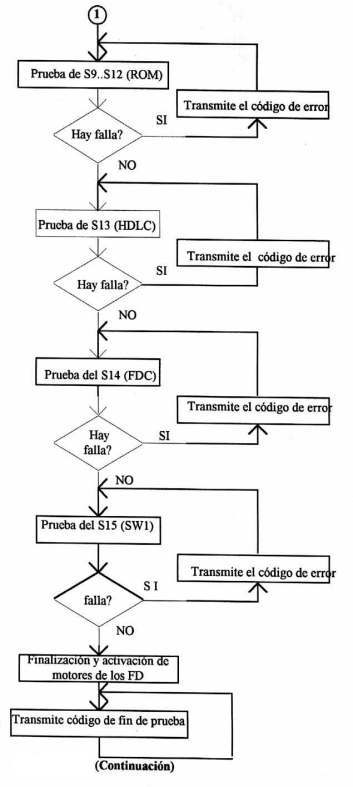

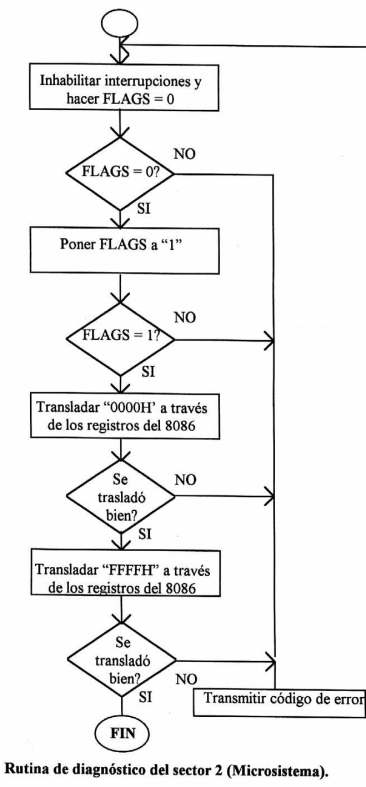

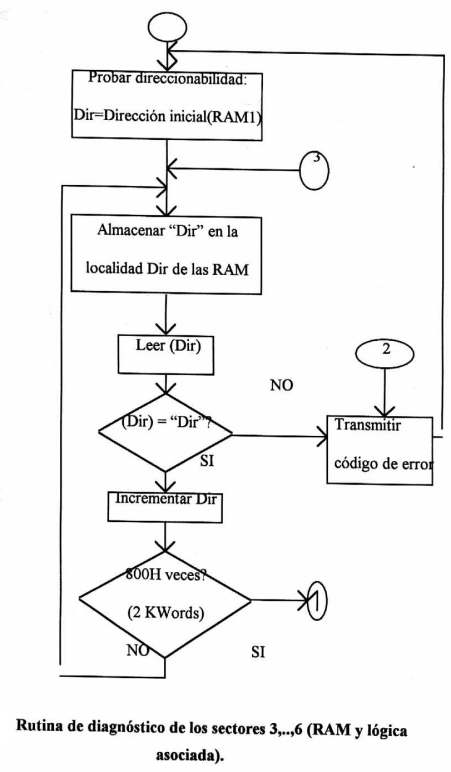

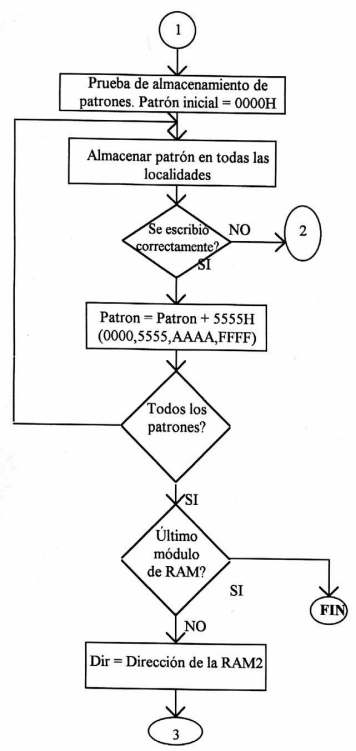

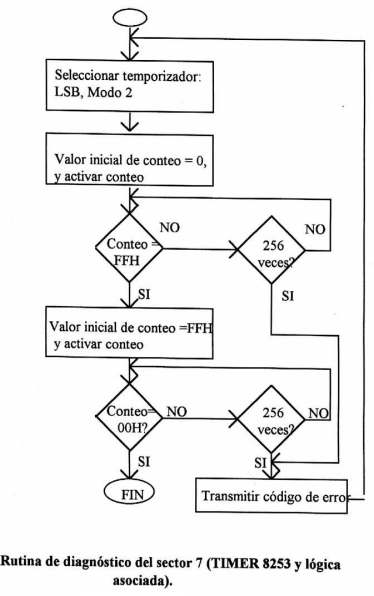

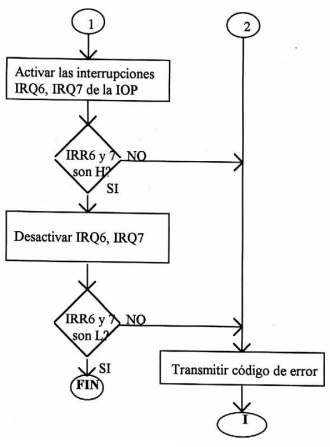

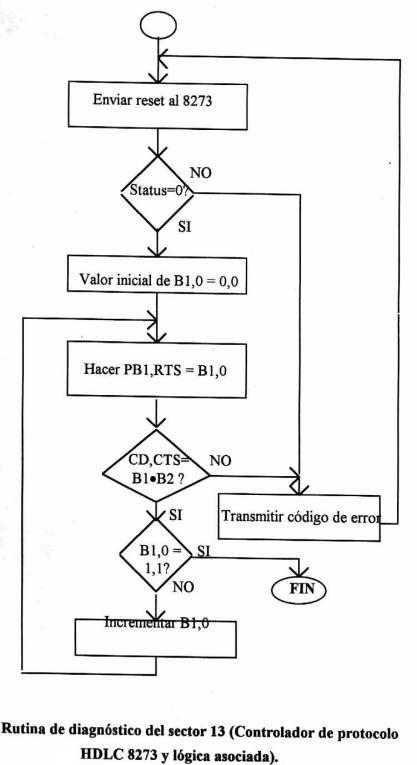

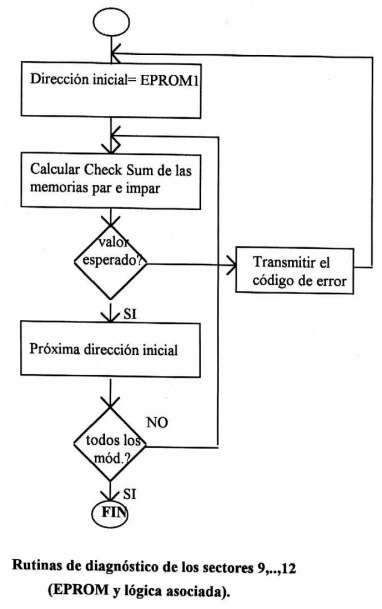

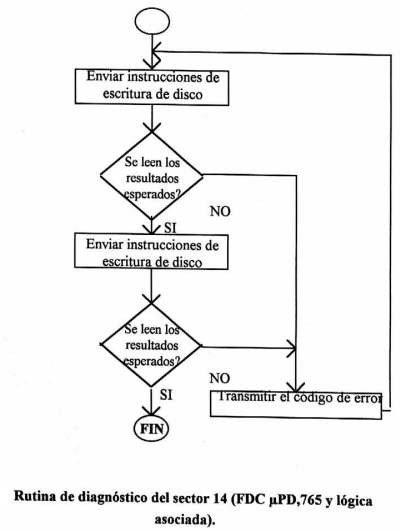

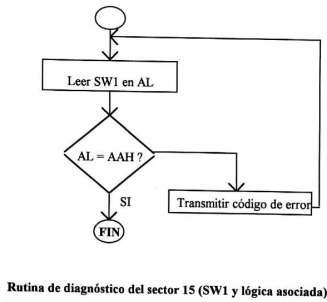

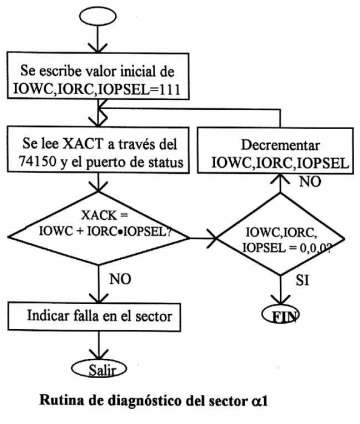

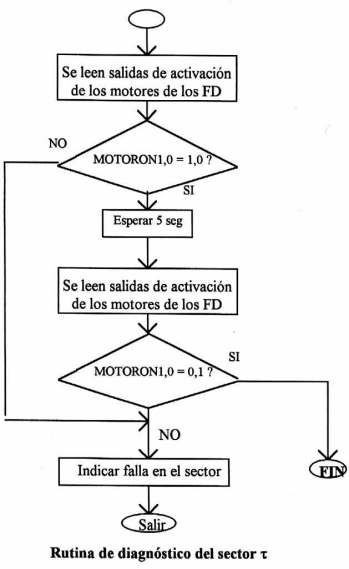

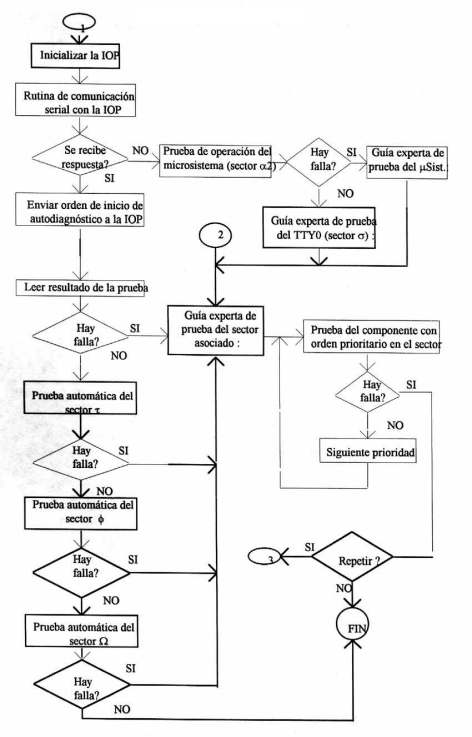

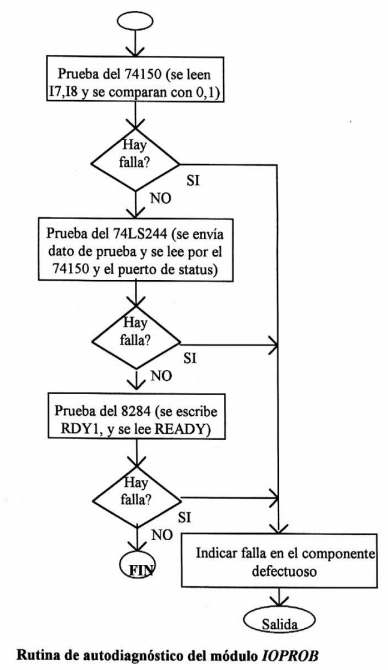

El firmware del sistema IOPROB consiste en un programa de bajo nivel, en lenguaje máquina del microprocesador 8086, que residirá en una EPROM que se insertará en el socket de la memoria fija principal de la tarjeta IOP, y tomará control de la misma, para realizar rutinas de autodiagnóstico de sus componentes principales (8086, 8089, 8253, 8259, 8273, µPD765, 8251, RAM y EPROM), que permitirán detectar las fallas en los distintos sectores de la tarjeta. Este programa recibirá algunas instrucciones del programa en alto nivel desde el PC, y le enviará información sobre el estado de la tarjeta, y las fallas detectadas. Este programa se está realizando con el ensamblador Turbo Assembler (TASM.EXE), de Borland. Una vez ensamblado el archivo fuente (IOPROB.ASM), se obtiene el archivo objeto (IOPROB.OBJ), el cual es enlazado con el programa enlazador Turbo Linker (TLINK.EXE), de Borland, generándose el archivo ejecutable (IOPROB.EXE), el cual es convertido en binario con el programa EXE2BIN del MS-DOS, obteniéndose finalmente el archivo binario (IOPROB.BIN), que puede ser grabado directamente en la EPROM. Esto último se hace con el Programador Universal SUPERPRO, seleccionando para la grabación el tipo de memoria INTEL 2716, y especificando un bús de 16 bits, con una memoria par y una impar (los bytes pares del programa se graban en una memoria y los bytes impares en otra). En el archivo de planos ioplans.zip, se presenta un diagrama de flujo (temporal) del programa en bajo nivel del sistema, y un listado parcial del mismo.

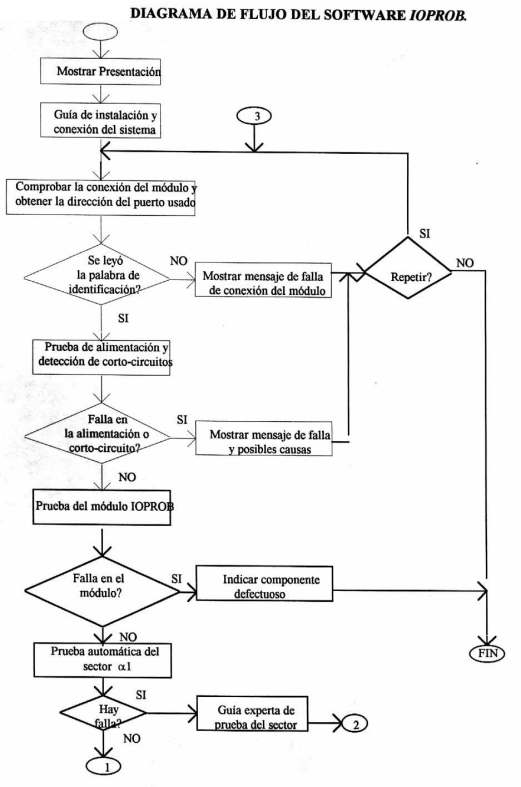

El software del sistema IOPROB se está realizando en el lenguaje de programación de alto nivel PASCAL, con el programa Turbo Pascal 7.0, de Borland. Se seleccionó este lenguaje para la programación de alto nivel del sistema experto, porque posee una amplia librería de instrucciones para manejo de la pantalla y el teclado, lo que permite realizar un buen diseño de los despliegues gráficos necesarios, e interactuar fácilmente con el usuario. Además, permite la creación y manejo de base de datos, necesarias para la creación del sistema experto, y brinda numerosas ventajas y facilidades para la programación de aplicaciones. Las rutinas de manejo de los puertos, envío y adquisición de datos, operaciones de control del módulo y procesamiento inicial de las señales de entrada y salida del mismo desde y hacia el PC, serán codificadas en lenguaje de bajo nivel (Assembler), para ser ejecutadas desde el PC, y serán enlazadas al programa principal de alto nivel, con la finalidad de manejar los recursos del hardware de una manera directa y veloz, como lo permite la programación en lenguaje de ensamble. Esta combinación de niveles en la programación desde el PC, aumentará la eficiencia del sistema experto, combinando las ventajas de la programación en alto nivel (procedimientos, funciones y rutinas preconcebidas, rutinas de manejo de los recursos del sistema: pantalla, teclado, unidad de disco, etc., acceso a las rutinas e interrupciones del DOS y del BIOS, etc.), con las de la programación en bajo nivel (acceso directo al hardware del sistema: puertos, registros, etc., mayor velocidad de ejecución), para determinadas aplicaciones. El programa se encarga del control de todas las acciones básicas del sistema, y de hacer la comunicación interactiva con el usuario, mostrándole los resultados de las operaciones de diagnóstico, e indicándole los pasos a seguir en la reparación, a través de los despliegues gráficos. En este DEMO se puede observar el funcionamiento del software, con condiciones iniciales de simulación de falla de comunicación.

La optimización del diagnóstico automático de fallas requirió de la creación de una metodología científica de pruebas.

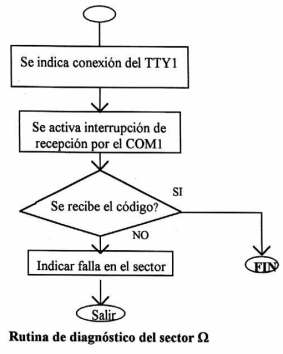

Para eso desarrollé la Teoría de Diagnóstico de Sistemas Complejos. Esta teoría permite generar listas ordenadas de zonas de prueba, con caminos óptimos de

búsqueda de fallas. A partir de los diagramas de pruebas por sectores, generé la base de datos del sistema experto. Mediante logs de historia de pruebas y falla, y

variables estadísticas dinámicas, el sistema tiene capacidad de aprendizaje automático, apoyado por motores de inferencia, herramientas de emulación

cognoscitivas y procedimientos de análisis y toma de decisiones, para los que escogí el procedimiento de algoritmos genéticos.